- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

Sic အစွန်းလက်စွပ်

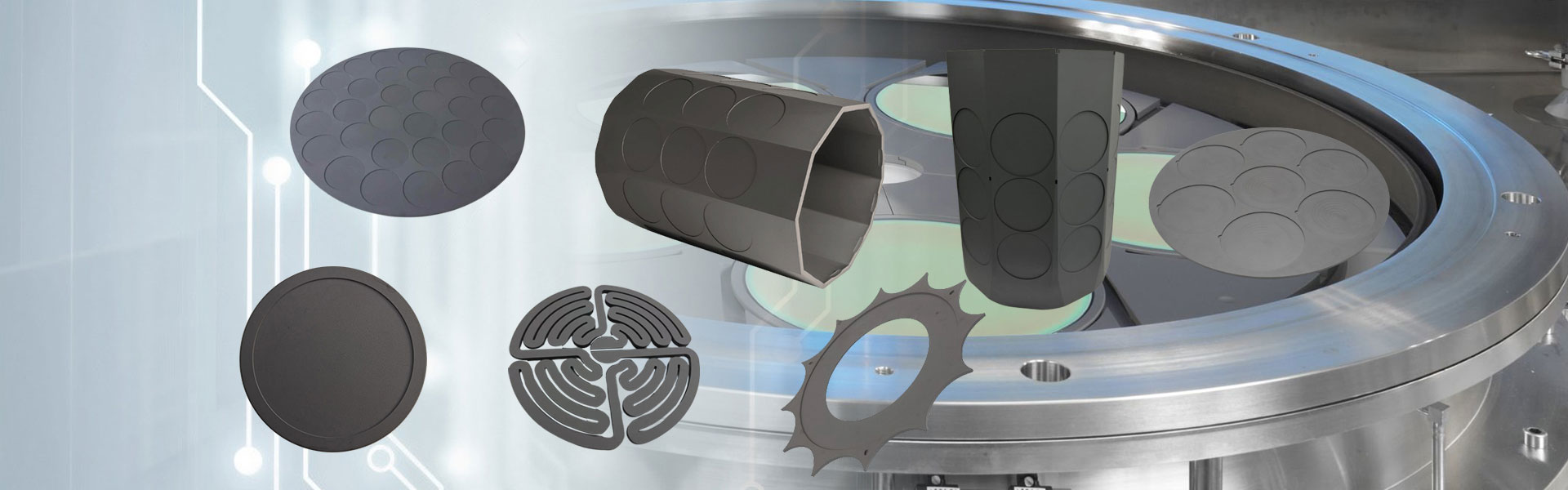

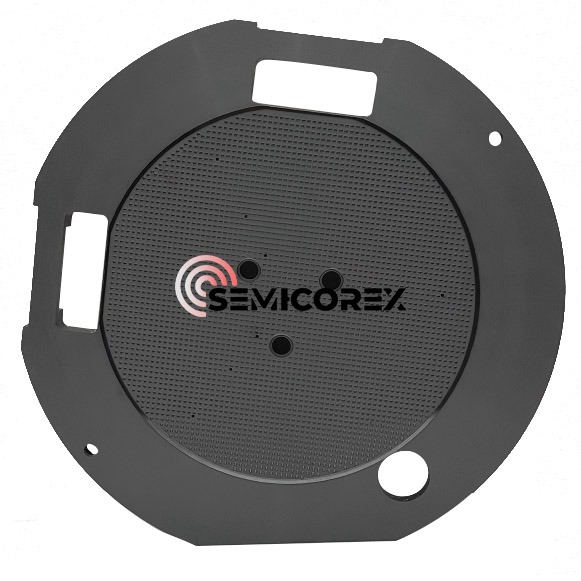

Semicorex CVD SIC EDEDED လက်စွပ်သည်စွမ်းဆောင်ရည်မြင့်မားသောပလာစမာနှင့်ရင်ဆိုင်နေရသည့်အစိတ်အပိုင်းဖြစ်ပြီးရှုပ်ထွေးသောစည်းလုံးညီညွတ်မှုကိုမြှင့်တင်ရန်နှင့် semiconductor ထုတ်လုပ်မှုတွင်ကာကွယ်ပေးသည်။ unmatched ပစ္စည်းများသန့်ရှင်းစင်ကြယ်ခြင်း,

စုံစမ်းမေးမြန်းရန်ပေးပို့ပါ။

Sememorex Sic Edge လက်စွပ် (CVD) silicon carbide (CVD) silicon carbide (SIC) Sicicon Carbide (SIC) ၏အရေးပါသောရှုထောင့်ကိုကိုယ်စားပြုသည်။ Plasma etching process စဉ်အတွင်း Extrostatic Chuck (Esc) ၏အပြင်ဘက်အစွန်းတွင်တည်ရှိသည်။

Semiconductor Integrated circuit (IC) ထုတ်လုပ်ခြင်းတွင်ပလာစမာ၏ယူနီဖောင်းဖြန့်ဖြူးခြင်းသည်အလွန်အရေးကြီးသည်။ Sic Edge Rain သည် Plasma ၏ယုံကြည်စိတ်ချရမှုနှစ်ခုစလုံးကို 0 င်ရောက်ယှဉ်ပြိုင်ခြင်းမရှိဘဲပေါင်နယ်နိမိတ်အတွင်းဆန့်ကျင်သောဆော့ဖ်အရင်းကိုတည်ငြိမ်စေစဉ်ပလာဗက်စ်၏ယုံကြည်စိတ်ချရမှုတွင်ပါ 0 င်ရန်အရေးကြီးသည်။

ဒီပလာစမာ actlaming လုပ်ငန်းစဉ်ကို Wafers များပေါ်တွင်ပြုလုပ်နေစဉ်ကွတ်များသည်စွမ်းအင်အိုင်းယွန်းများမှဗုံးကြဲတိုက်ခိုက်မှုနှင့်ထိတွေ့မှုနှင့်ထိတွေ့မှုနှင့်ထိတွေ့မှုနှင့်ထိတွေ့မှုနှင့်အတူတုန့်ပြန်ဓာတ်ငွေ့များကိုသွေးသွင်းနိုင်သည့်ဓာတ်ငွေ့များဖြင့်ပါ 0 င်သည်။ ဤအခြေအနေများသည်မှန်ကန်စွာမနိုင်ပါကရှုပ်ထွေးသောနှင့် wafer အစွန်းအရည်အသွေးကိုဆိုးကျိုးသက်ရောက်နိုင်သည့်မြင့်မားသောစွမ်းအင်သိပ်သည်းဆလုပ်ငန်းစဉ်များကိုဖန်တီးနိုင်သည်။ အစွန်းလက်စွပ်ကို Wafer ပြုပြင်ထုတ်လုပ်မှု၏အခြေအနေနှင့်အတူပူးပေါင်းနိုင်ပြီးလျှပ်စစ်ထုတ်လွှင့်ပလာစမာ၏မီးလောင်မှုအနေဖြင့်စုပ်စက်များပေါ်ပေါက်လာသောမီးလက်စွပ်ကိုစုပ်ယူပြီးလျှပ်စစ်လယ်ကွင်းရှိစွမ်းအင်ကိုစုပ်ယူပြီးမီးစက်မှ ESC အထိထိရောက်သောထိရောက်မှုကိုဖြန့်ဝေပေးလိမ့်မည်။ ဤတည်ငြိမ်မှုကိုနည်းအမျိုးမျိုးဖြင့်အသုံးပြုသည်။ Plasma ယိုစိမ့်မှုပမာဏကိုလျှော့ချခြင်းနှင့်စုပ်စက်နယ်နိမိတ်အစွန်းအနီးရှိပုံပျက်မှုပမာဏကိုလျှော့ချခြင်းအပါအ 0 င်နည်းအမျိုးမျိုးဖြင့်အသုံးပြုသည်။

မျှတသောပလာစမာပတ်ဝန်းကျင်ကိုမြှင့်တင်ခြင်းအားဖြင့် Sic Eduction လက်စွပ်သည် micro-loading effect များကိုလျှော့ချရန်, ၎င်းသည်ပိုမိုမြင့်မားသောလုပ်ငန်းစဉ်ကိုထပ်ခါတလဲလဲလုပ်နိုင်မှုကိုပိုမိုမြန်ဆန်စေနိုင်သည်။

ရပ်တန့်သွားခြင်းကိုတစ် ဦး နှင့်တစ် ဦး ချိတ်ဆက်ထားပြီး, ဥပမာအားဖြင့်လျှပ်စစ်ရပ်တည်မှုသည်အိမ်မှ shapehology ၏ပုံပျက်ခြင်းကိုပုံပျက်စေပြီးအဖြစ်အပျက်များကိုပြောင်းလဲစေခြင်းငှါပုံဖော်ခြင်းကိုဖြစ်ပေါ်စေသည်။ အပူချိန်အကွက်သည်ဓာတုဓာတ်ပြုမှုနှုန်းကိုအကျိုးသက်ရောက်စေနိုင်သည်, အစွန်း etching နှုန်းကိုဗဟို area ရိယာမှသွေဖည်သွားစေနိုင်သည်။ အထက်ပါစိန်ခေါ်မှုများကိုတုံ့ပြန်ခြင်းသည်များသောအားဖြင့်တိုးတက်မှုများကိုများသောအားဖြင့်ရှုထောင့်နှစ်ခုဖြင့်ပြုလုပ်လေ့ရှိသည်။

အာရုံစိုက်သည့်လက်စွပ်သည် Wafer Edge abeting ၏တူညီမှုကိုတိုးတက်စေရန်အဓိကအစိတ်အပိုင်းဖြစ်သည်။ ၎င်းသည်ပလာစမာဖြန့်ဖြူးရေး area ရိယာကိုချဲ့ထွင်ရန်နှင့် Shake Morphyology ကိုပိုမိုကောင်းမွန်စေရန် Wafer ၏အစွန်းအစွန်းတွင်တပ်ဆင်ထားသည်။ အာရုံစူးစိုက်မှု၏မရှိခြင်း၌ Wafer Edge နှင့်လျှပ်ကူးပစ္စည်းအကြားအမြင့်ခြားနားချက်သည်အိမ်တော်ကိုကွေးစေလွှတ်။ မယူနီဖောင်းမဟုတ်သောထောင့်တွင် onling area ရိယာသို့ 0 င်ရောက်ခြင်းကိုဖြစ်ပေါ်စေသည်။

အာရုံဆိုင်၏လုပ်ဆောင်ချက်များကိုပါဝင်သည်:

• Wafer Edge နှင့် Electrope တို့အကြားအမြင့်ခြားနားချက်ကိုဖြည့်စွက်ခြင်း, အိုင်းယွန်းများသည်အိုင်းရစ်သံကိုဖြည့်ဆည်းပေးပြီးအိုင်းယွန်းများသည် wafer မျက်နှာပြင်ကိုဒေါင်လိုက်ထိုးခြင်းနှင့်ပုံပျက်မှုကိုရှောင်ရှားရန်သေချာစေသည်။

•စည်းလုံးညီညွတ်မှုကိုတိုးတက်အောင်လုပ်ခြင်းနှင့်အလွန်အကျွံအစွန်း etching သို့မဟုတ်စောင်း actloting profile အဖြစ်ပြ problems နာများကိုလျှော့ချပါ။

ပစ္စည်းအားသာချက်များ

CVD SIC အသုံးပြုမှုကိုအခြေခံပစ္စည်းသည်ရိုးရာကြွေထည်သို့မဟုတ် coated ပစ္စည်းများအပေါ်အားသာချက်များစွာကိုပေးသည်။ CVD SIC သည်ဓာတုဗေဒအရ inert, အပူတည်ငြိမ်မှုနှင့်အလွန်အမင်းတည်ငြိမ်မှုကိုခံနိုင်ရည်ရှိခြင်းနှင့်ကလိုရင်းအခြေစိုက်သမားများနှင့်ကလိုရင်းအခြေစိုက်ဓာတုပစ္စည်းများ၌ပင်ပလာစမာတိုက်စားမှုကိုခံနိုင်ရည်ရှိသည်။ ၎င်း၏အလွန်ကောင်းမွန်သောစက်ပိုင်းဆိုင်ရာစွမ်းအားနှင့်ရှုထောင့်များတည်ငြိမ်မှုသည် 0 န်ဆောင်မှုသက်တမ်းသည်အပူချိန်မြင့်မားသောစက်ဘီးစီးသည့်အခြေအနေများအောက်တွင်အမှုန်သက်တောင့်သက်သာရှိစေရန်သေချာစေသည်။

ထို့အပြင် CVD SIC SIC ၏ Ultra-cerructructs သည်ညစ်ညမ်းမှုအန္တရာယ်ကိုလျော့နည်းစေသည်။ SASS ESC ပလက်ဖောင်းများနှင့်ဗဟိုပလက်ဖောင်းများနှင့်သဟဇာတဖြစ်သောသဟဇာတဖြစ်သော ercber chamber Geometries သည်အဆင့်မြင့် 200 မီလီမီတာနှင့် 300mm abeting tools များနှင့်အတူချောမွေ့စွာပေါင်းစည်းမှုကိုခွင့်ပြုသည်။