- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

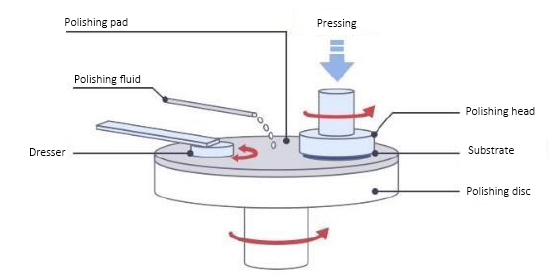

CMP Process ကိုဘယ်လိုလုပ်မလဲ။

CMP လုပ်ငန်းစဉ်-

1. ပြင်ပါ။waferပွတ်ဆေးခေါင်း၏အောက်ခြေတွင်၊ ပွတ်ဆေးပြားကို ကြိတ်ထားသောအပြားပေါ်တွင် တင်ပါ။

2. လှည့်နေသော ပေါလစ်တိုက်ခေါင်းသည် လှည့်နေသော ပွတ်ပွတ်ပြားပေါ်တွင် အချို့သော ဖိအားဖြင့် ဖိထားပြီး၊ နာနိုပွန်းပဲ့သော အမှုန်အမွှားများနှင့် ဓာတုဗေဒအရည်များ ပေါင်းစပ်ထားသည့် စီးဆင်းနေသော ကြိတ်ရည်ကို ဆီလီကွန် wafer မျက်နှာပြင်နှင့် ပေါလစ်ပွတ်ချပ်ကြားတွင် ပေါင်းထည့်ပါသည်။ ကြိတ်ချေထားသောအရည်ကို ပွတ်စင်ပြား၏ ပို့လွှတ်မှုအောက်တွင် အညီအမျှ ဖုံးအုပ်ထားပြီး၊ ဆီလီကွန်ဝေဖာနှင့် ပွတ်ချပ်ကြားရှိ အရည်ဖလင်တစ်ခုအဖြစ် ပေါင်းစပ်ထားသည်။

3. Flattening သည် ဓာတုဖလင်ဖယ်ထုတ်ခြင်းနှင့် စက်ပိုင်းဆိုင်ရာ ရုပ်ရှင်ဖယ်ရှားခြင်း၏ တလှည့်စီလုပ်ငန်းစဉ်အားဖြင့် အောင်မြင်သည်။

CMP ၏ အဓိက နည်းပညာဆိုင်ရာ ဘောင်များ-

ကြိတ်နှုန်း- ယူနစ်အချိန်အလိုက် ဖယ်ရှားထားသော ပစ္စည်း၏ အထူ။

Flatness- (စီလီကွန် wafer/ CMP မတိုင်မီ ခြေလှမ်းအမြင့်တွင် CMP ရှေ့နှင့်နောက် အကြား ခြားနားချက်) * 100%

ကြိတ်ခွဲမှု တူညီမှု- ဆပ်ပြာအတွင်းပိုင်း တူညီမှုနှင့် ဆပ်ပြာကြား တူညီမှု အပါအဝင်။ Intra-wafer တူညီမှုသည် ဆီလီကွန် wafer တစ်ခုတည်းရှိ မတူညီသော ရာထူးများတွင် ကြိတ်ချေမှုနှုန်း၏ ညီညွတ်မှုကို ရည်ညွှန်းသည်။ inter-wafer တူညီမှုသည် တူညီသော CMP အခြေအနေများအောက်တွင် မတူညီသော ဆီလီကွန် wafers များအကြား ကြိတ်ခွဲမှုနှုန်းကို ရည်ညွှန်းသည်။

ချို့ယွင်းချက်ပမာဏ- CMP လုပ်ငန်းစဉ်အတွင်း ထုတ်ပေးသည့် မျက်နှာပြင်ချို့ယွင်းချက်အမျိုးမျိုး၏ အရေအတွက်နှင့် အမျိုးအစားကို ရောင်ပြန်ဟပ်စေပြီး၊ ၎င်းသည် ဆီမီးကွန်ဒတ်တာကိရိယာများ၏ စွမ်းဆောင်ရည်၊ ယုံကြည်စိတ်ချရမှုနှင့် အထွက်နှုန်းတို့ကို ထိခိုက်စေမည်ဖြစ်သည်။ အဓိကအားဖြင့် ခြစ်ရာများ၊ စိတ်ဓာတ်ကျခြင်း၊ တိုက်စားခြင်း၊ အကြွင်းအကျန်များနှင့် အမှုန်အမွှားများ အပါအဝင်ဖြစ်သည်။

CMP လျှောက်လွှာများ

ဆီမီးကွန်ဒတ်တာ ထုတ်လုပ်မှု လုပ်ငန်းစဉ်တစ်ခုလုံးတွင်၊ဆီလီကွန် waferထုတ်လုပ်ခြင်း၊ wafer ထုတ်လုပ်မှု၊ ထုပ်ပိုးခြင်းအထိ CMP လုပ်ငန်းစဉ်ကို ထပ်ခါတလဲလဲ အသုံးပြုရန် လိုအပ်ပါသည်။

ဆီလီကွန် waferထုတ်လုပ်မှုလုပ်ငန်းစဉ်တွင်၊ crystal rod ကို silicon wafers များအဖြစ်ဖြတ်ပြီးနောက်၊ မှန်ကဲ့သို့ crystal silicon wafer တစ်ခုတည်းရရှိရန်၎င်းကိုပွတ်တိုက်ပြီးသန့်ရှင်းရန်လိုအပ်သည်။

wafer ထုတ်လုပ်မှုလုပ်ငန်းစဉ်တွင်၊ အိုင်းယွန်းထည့်သွင်းခြင်း၊ ပါးလွှာသောဖလင်များထည့်ခြင်း၊ ပုံသဏ္ဍာန်ပြုလုပ်ခြင်း၊ ထွင်းထုခြင်းနှင့် အလွှာပေါင်းစုံ ဝါယာကြိုးများချိတ်ဆက်ခြင်းများ ပြုလုပ်ခြင်းဖြင့် ကုန်ထုတ်လုပ်မှု၏မျက်နှာပြင်အလွှာတစ်ခုစီသည် နာနိုမီတာအဆင့်တွင် ကမ္ဘာလုံးဆိုင်ရာပြားချပ်ချပ်များရရှိစေရန် သေချာစေရန်အတွက် မကြာခဏအသုံးပြုရန် လိုအပ်ပါသည်။ CMP လုပ်ငန်းစဉ်ကို အကြိမ်ကြိမ်။

အဆင့်မြင့်ထုပ်ပိုးမှုနယ်ပယ်တွင်၊ CMP လုပ်ငန်းစဉ်များကို အမြောက်အမြားစတင်မိတ်ဆက်ပြီး အသုံးပြုလာကြပြီး ၎င်းတို့တွင် ဆီလီကွန်နည်းပညာမှတစ်ဆင့် (TSV)၊ ပန်ကာထုတ်ခြင်း၊ 2.5D၊ 3D ထုပ်ပိုးမှုစသည်ဖြင့် CMP လုပ်ငန်းစဉ်အများအပြားကို အသုံးပြုမည်ဖြစ်သည်။

ပွတ်ဆေးအမျိုးအစားအရ၊ ကျွန်ုပ်တို့သည် CMP ကို သုံးမျိုးခွဲထားသည်။

1. Substrate၊ အဓိကအားဖြင့် ဆီလီကွန်ပစ္စည်း

2. အလူမီနီယမ်/ကြေးနီသတ္တု အပြန်အလှန်ချိတ်ဆက်သည့်အလွှာအပါအဝင် သတ္တု၊ Ta/Ti/TiN/TiNxCy နှင့် အခြားပျံ့နှံ့မှုအတားအဆီးအလွှာများ၊ တွယ်တာမှုအလွှာ။

3. SiO2၊ BPSG၊ PSG၊ SI3N4/SiOxNy ကဲ့သို့သော passivation အလွှာများနှင့် အတားအဆီးအလွှာများ အပါအဝင် ဒိုင်ယာလျှပ်စစ်များ။