- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

CMP Process ဆိုတာဘာလဲ

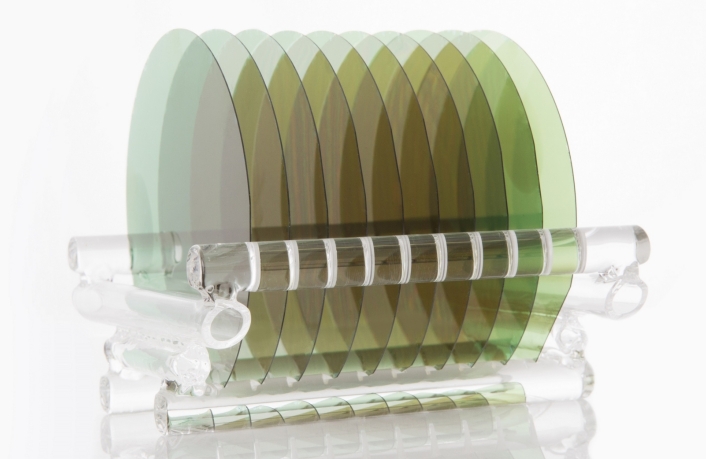

တစ်ပိုင်းလျှပ်ကူးပစ္စည်းထုတ်လုပ်ခြင်းတွင်၊ အက်တမ်အဆင့် ပြားချပ်ချပ်ကို အများအားဖြင့် ကမ္ဘာလုံးဆိုင်ရာ ပြားချပ်ချပ်မှုဖော်ပြရန် အသုံးပြုသည်။waferနာနိုမီတာ (nm) ယူနစ်ဖြင့်၊ အကယ်၍ ကမ္ဘာလုံးဆိုင်ရာပြားချပ်ချပ်လိုအပ်ချက်သည် 10 nanometers (nm) ဖြစ်ပါက၊ ၎င်းသည် ဧရိယာ 1 စတုရန်းမီတာတွင် 10 nanometer အမြင့်ခြားနားချက်နှင့် ညီမျှသည် (10nm ကမ္ဘာလုံးဆိုင်ရာပြားချပ်ချပ်သည် Tiananmen Square ရှိ မည်သည့်အမှတ်နှစ်ခုကြားမှ အမြင့်ကွာခြားချက်နှင့် ညီမျှသည်။ ဧရိယာ 440,000 စတုရန်းမီတာရှိသော 30 microns ထက်မပိုပါ။) နှင့် ၎င်း၏ မျက်နှာပြင် ကြမ်းတမ်းမှုသည် 0.5 မီလီမီတာ (အချင်း 75 မိုက်ခရိုရွန်ရှိသော ဆံပင်နှင့် နှိုင်းယှဉ်ပါက ဆံပင်၏ 150,000 ပုံတစ်ပုံနှင့် ညီမျှသည်)။ မညီမညာမှုများသည် ဝါယာရှော့ဖြစ်ပြီး ဆားကစ်ပြတ်တောက်ခြင်း သို့မဟုတ် စက်၏ယုံကြည်စိတ်ချရမှုကို ထိခိုက်စေနိုင်သည်။ ဤမြင့်မားသော တိကျပြတ်သားမှု လိုအပ်ချက်သည် CMP ကဲ့သို့သော လုပ်ငန်းစဉ်များဖြင့် အောင်မြင်ရန် လိုအပ်ပါသည်။

CMP လုပ်ငန်းစဉ်နိယာမ

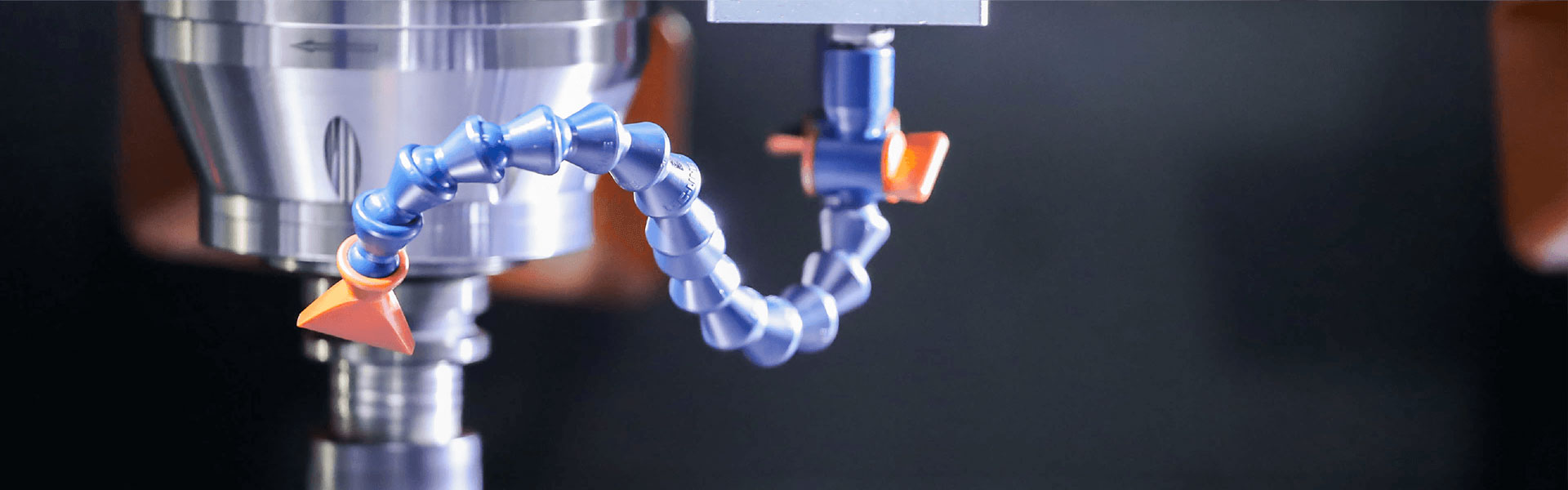

Chemical Mechanical Polishing (CMP) သည် ဆီမီးကွန်ဒတ်တာ ချစ်ပ်ထုတ်လုပ်နေစဉ်အတွင်း wafer မျက်နှာပြင်ကို ပြားစေသည့် နည်းပညာတစ်ခုဖြစ်သည်။ ပွတ်ရည်နှင့် wafer မျက်နှာပြင်ကြားတွင် ဓာတုတုံ့ပြန်မှုမှတစ်ဆင့် ကိုင်တွယ်ရလွယ်ကူသော အောက်ဆိုဒ်အလွှာတစ်ခု ထုတ်ပေးသည်။ ထို့နောက် အောက်ဆိုဒ်အလွှာ၏ မျက်နှာပြင်ကို စက်ဖြင့် ကြိတ်ချေသည်။ ဓာတုနှင့် စက်ပိုင်းဆိုင်ရာ လုပ်ဆောင်ချက်များစွာကို တစ်လှည့်စီလုပ်ဆောင်ပြီးနောက်၊ ယူနီဖောင်းနှင့် ပြားချပ်သော wafer မျက်နှာပြင်ကို ဖွဲ့စည်းသည်။ wafer မျက်နှာပြင်မှ ဖယ်ရှားလိုက်သော ဓာတု ဓာတ်ပြုပစ္စည်းများသည် စီးဆင်းနေသော အရည်တွင် ပျော်ဝင်ပြီး ဖယ်ထုတ်ခြင်း ဖြစ်သောကြောင့် CMP polishing လုပ်ငန်းစဉ်တွင် ဓာတုနှင့် ရုပ်ပိုင်းဆိုင်ရာ လုပ်ငန်းစဉ် နှစ်ခု ပါဝင်ပါသည်။