- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

ဆီလီကွန် wafer မျက်နှာပြင်ကို အပြီးသတ် ပွတ်ခြင်း။

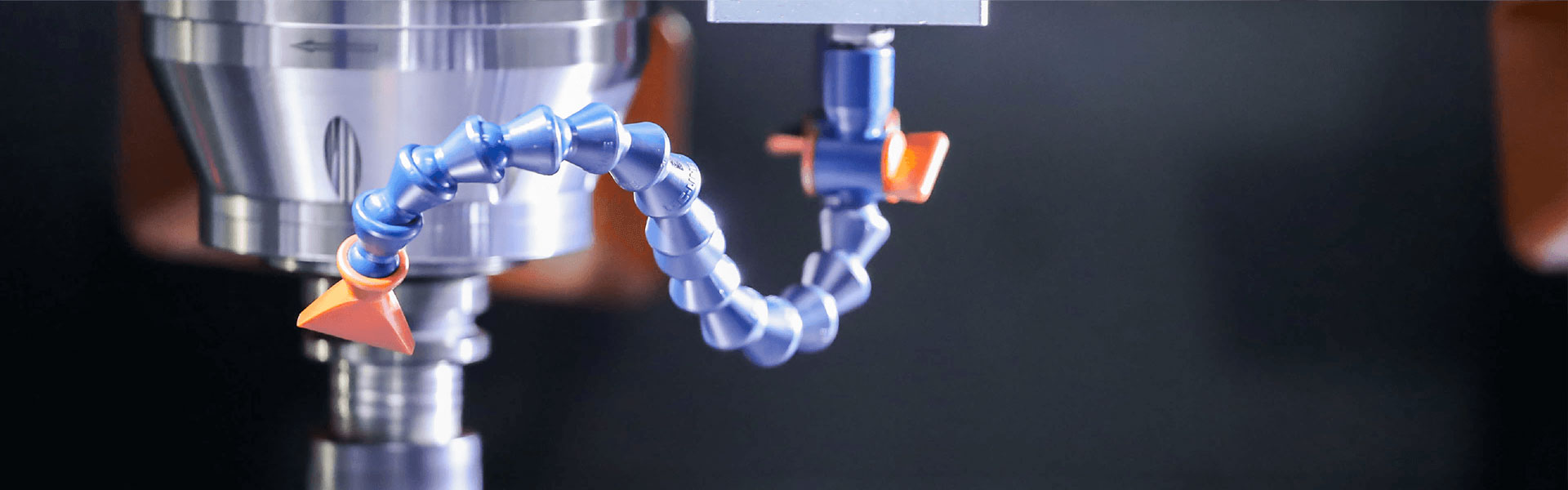

300mm အချင်းဆီလီကွန်ပွတ်ဆပ်ပြာမှုန့်များအတွက် 0.13μm မှ 28nm ထက်ငယ်သော IC ချစ်ပ်ဆားကစ်လုပ်ငန်းစဉ်များ၏ အရည်အသွေးမြင့်လိုအပ်ချက်များကို ရရှိစေရန်၊ wafer ၏မျက်နှာပြင်ပေါ်ရှိ သတ္တုအိုင်းယွန်းများကဲ့သို့သော အညစ်အကြေးများမှ ညစ်ညမ်းမှုကို လျှော့ချရန် မရှိမဖြစ်လိုအပ်ပါသည်။ ထို့ အပြင်၊ဆီလီကွန် waferအလွန်မြင့်မားသော မျက်နှာပြင် nanomorphology လက္ခဏာများ ပြသရပါမည်။ ရလဒ်အနေဖြင့် နောက်ဆုံးပေါ်လစ်တိုက်ခြင်း (သို့မဟုတ် ချောမွတ်ခြင်း) သည် လုပ်ငန်းစဉ်တွင် အရေးကြီးသော အဆင့်တစ်ခု ဖြစ်လာသည်။

ဤနောက်ဆုံးပေါ်လစ်တိုက်ခြင်းသည် ပုံမှန်အားဖြင့် အယ်ကာလိုင်းကော်လိုဒိုင်းဆီလီကာဓာတုဗေဒစက်မှုပွတ်ခြင်း (CMP) နည်းပညာကို အသုံးပြုသည်။ ဤနည်းလမ်းသည် သေးငယ်သော မစုံလင်မှုနှင့် အညစ်အကြေးများကို ထိထိရောက်ရောက်နှင့် တိကျစွာဖယ်ရှားရန် ဓာတုချေးနှင့် စက်ပွန်းပဲ့ခြင်း၏ အာနိသင်များကို ပေါင်းစပ်ထားသည်။ဆီလီကွန် waferမျက်နှာပြင်။

သို့ရာတွင် ရိုးရာ CMP နည်းပညာသည် ထိရောက်သော်လည်း ပစ္စည်းကိရိယာများသည် စျေးကြီးနိုင်ပြီး သေးငယ်သောမျဉ်းအကျယ်များအတွက် လိုအပ်သော တိကျမှုကို ရရှိရန်မှာ သမားရိုးကျ ပွတ်တိုက်သည့်နည်းလမ်းများဖြင့် စိန်ခေါ်မှုဖြစ်နိုင်သည်။ ထို့ကြောင့် စက်မှုလုပ်ငန်းသည် ဒစ်ဂျစ်တယ်ထိန်းချုပ်ထားသော ဆီလီကွန်ဝေဖာများအတွက် ခြောက်သွေ့သောဓာတုဗေဒပလာစမာပလာစမာနည်းပညာ (D.C.P. ပလာစမာနည်းပညာ) ကဲ့သို့သော ပွတ်ခြင်းနည်းပညာအသစ်များကို ရှာဖွေနေပါသည်။

![]()

D.C.P ပလာစမာနည်းပညာသည် အဆက်အသွယ်မရှိသော လုပ်ဆောင်မှုနည်းပညာတစ်ခုဖြစ်သည်။ ၎င်းသည် SF6 (ဆာလဖာ ဟက်ဆာဖလိုရိုက်) ပလာစမာကို အသုံးပြု၍ ၎င်းကို ခြစ်ထုတ်သည်။ဆီလီကွန် waferမျက်နှာပြင်။ တိကျစွာ plasma etching processing time ကိုထိန်းချုပ်ခြင်းဖြင့်ဆီလီကွန် waferစကင်န်ဖတ်ခြင်းမြန်နှုန်းနှင့် အခြားသော ကန့်သတ်ချက်များ၊ ၎င်းသည် မြင့်မားသော တိကျပြတ်သားမှုကို ရရှိစေနိုင်သည်။ဆီလီကွန် waferမျက်နှာပြင်။ သမားရိုးကျ CMP နည်းပညာနှင့် နှိုင်းယှဉ်ပါက D.C.P နည်းပညာသည် ပိုမိုကောင်းမွန်သော လုပ်ဆောင်ချက်တိကျမှုနှင့် တည်ငြိမ်မှုရှိပြီး ပွတ်တိုက်မှုကုန်ကျစရိတ်ကို သိသိသာသာ လျှော့ချနိုင်သည်။

D.C.P လုပ်ငန်းစဉ်အတွင်း၊ အောက်ပါနည်းပညာဆိုင်ရာ ပြဿနာများအတွက် အထူးအာရုံစိုက်ရန် လိုအပ်သည်-

ပလာစမာရင်းမြစ်ကို ထိန်းချုပ်ခြင်း- SF ကဲ့သို့သော ကန့်သတ်ချက်များကို သေချာပါစေ။6(ပလာစမာမျိုးဆက်နှင့် အလျင်စီးဆင်းမှုပြင်းထန်မှု၊ အလျင်စီးဆင်းမှုအချင်း (အလျင်စီးဆင်းမှုကို အာရုံစူးစိုက်မှု)) သည် ဆီလီကွန် wafer ၏မျက်နှာပြင်ပေါ်ရှိ တစ်ပြေးညီချေးများရရှိစေရန် တိကျစွာထိန်းချုပ်ထားသည်။

စကင်န်ဖတ်ခြင်းစနစ်၏ တိကျမှုကို ထိန်းချုပ်ခြင်း- X-Y-Z တွင်ရှိသော စကင်န်ဖတ်စနစ်သည် ဆီလီကွန် wafer ၏ သုံးဖက်မြင် လမ်းညွှန်မှုတွင် အလွန်မြင့်မားသော ထိန်းချုပ်မှု တိကျမှု ရှိရန် လိုအပ်ပါသည်။

နည်းပညာသုတေသနလုပ်ဆောင်ခြင်း- D.C.P ပလာစမာနည်းပညာ၏ လုပ်ငန်းစဉ်အတွင်း နက်ရှိုင်းသောသုတေသနနှင့် ပိုမိုကောင်းမွန်အောင်ပြုလုပ်ခြင်းတို့သည် အကောင်းဆုံးလုပ်ဆောင်ခြင်းဆိုင်ရာ ကန့်သတ်ချက်များနှင့် အခြေအနေများကို ရှာဖွေရန် လိုအပ်ပါသည်။

မျက်နှာပြင်ပျက်စီးမှုကို ထိန်းချုပ်ခြင်း- D.C.P လုပ်ငန်းစဉ်အတွင်း၊ IC ချစ်ပ်ဆားကစ်များ၏ နောက်ဆက်တွဲပြင်ဆင်မှုအပေါ် ဆိုးကျိုးများမဖြစ်စေရန် ဆီလီကွန်ဝေဖာ၏ မျက်နှာပြင်ပေါ်ရှိ ပျက်စီးမှုများကို တင်းကြပ်စွာ ထိန်းချုပ်ထားရန် လိုအပ်ပါသည်။

D.C.P ပလာစမာနည်းပညာတွင် အားသာချက်များစွာရှိသော်လည်း ၎င်းသည် ပြုပြင်ဆဲနည်းပညာအသစ်ဖြစ်သောကြောင့်၊ ၎င်းသည် သုတေသနနှင့် ဖွံ့ဖြိုးတိုးတက်ရေးအဆင့်တွင်သာ ရှိသေးသည်။ ထို့ကြောင့်၊ ၎င်းကို လက်တွေ့အသုံးချမှုများတွင် သတိဖြင့် ကုသရန် လိုအပ်ပြီး နည်းပညာပိုင်းဆိုင်ရာ တိုးတက်မှုနှင့် အကောင်းဆုံးဖြစ်အောင် ဆက်လက်လုပ်ဆောင်ရန် လိုအပ်ပါသည်။

![]()

ယေဘူယျအားဖြင့် နောက်ဆုံးပေါ်လစ်ပွတ်ခြင်းသည် အရေးကြီးသော အစိတ်အပိုင်းတစ်ခုဖြစ်သည်။ဆီလီကွန် waferလုပ်ဆောင်ခြင်းလုပ်ငန်းစဉ်၊ ၎င်းသည် IC ချစ်ပ်ပတ်လမ်း၏ အရည်အသွေးနှင့် စွမ်းဆောင်ရည်တို့နှင့် တိုက်ရိုက်သက်ဆိုင်သည်။ ဆီမီးကွန်ဒတ်တာစက်မှုလုပ်ငန်း၏စဉ်ဆက်မပြတ်ဖွံ့ဖြိုးတိုးတက်မှုနှင့်အတူ, အရည်အသွေးလိုအပ်ချက်များ၏မျက်နှာပြင်ဆီလီကွန် wafersပိုမြင့်လာမယ်။ ထို့ကြောင့်၊ တောက်လျှောက်နည်းပညာအသစ်များကို စဉ်ဆက်မပြတ် ရှာဖွေဖော်ထုတ်ခြင်းသည် အနာဂတ်တွင် ဆီလီကွန် wafer ပြုပြင်ခြင်းနယ်ပယ်တွင် အရေးကြီးသော သုတေသနလမ်းညွှန်ချက်တစ်ခု ဖြစ်လာမည်ဖြစ်သည်။

Semicorex ကမ်းလှမ်းချက်များအရည်အသွေးမြင့် wafers. သင့်တွင် စုံစမ်းမေးမြန်းမှုများ သို့မဟုတ် နောက်ထပ်အသေးစိတ်အချက်အလက်များ လိုအပ်ပါက၊ ကျွန်ုပ်တို့ထံ ဆက်သွယ်ရန် တုံ့ဆိုင်းမနေပါနှင့်။

ဖုန်း # +86-13567891907 သို့ ဆက်သွယ်နိုင်ပါသည်။

အီးမေးလ်- sales@semicorex.com