- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

ဆီလီကွန် Wafer

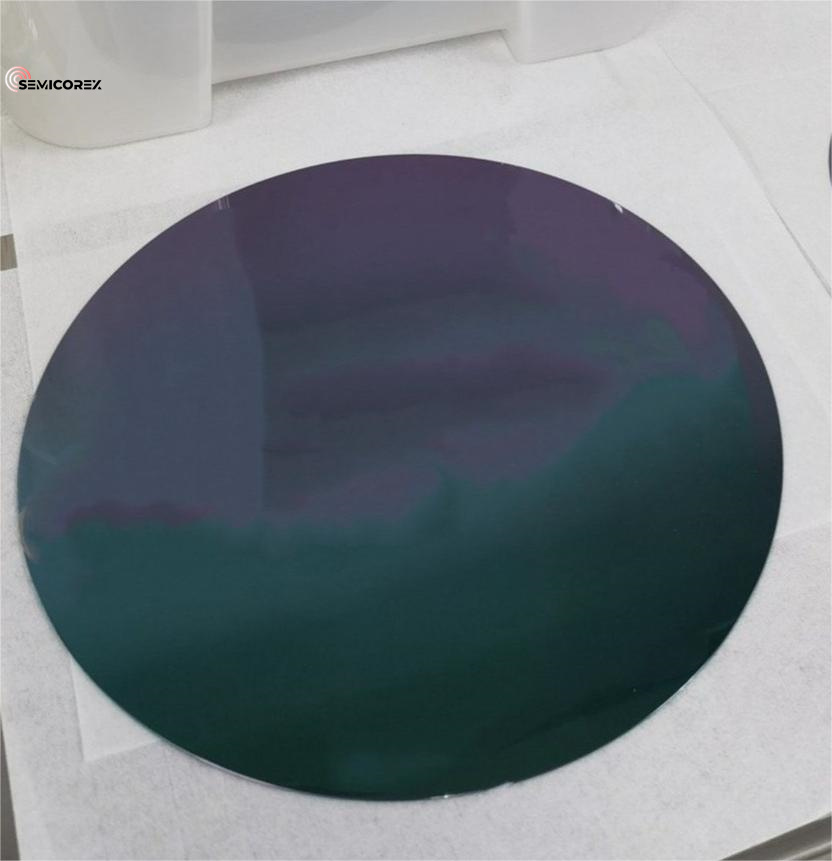

ဆီလီကွန်ပစ္စည်းသည် အချို့သော semiconductor လျှပ်စစ်ဂုဏ်သတ္တိများနှင့် ရုပ်ပိုင်းဆိုင်ရာတည်ငြိမ်မှုရှိသော အစိုင်အခဲပစ္စည်းဖြစ်ပြီး၊ နောက်ဆက်တွဲပေါင်းစပ်ပတ်လမ်းထုတ်လုပ်မှုလုပ်ငန်းစဉ်အတွက် အောက်စထရိအား ပံ့ပိုးပေးပါသည်။ ၎င်းသည် ဆီလီကွန်အခြေခံ ပေါင်းစည်းထားသော ဆားကစ်များအတွက် အဓိကပစ္စည်းဖြစ်သည်။ ကမ္ဘာပေါ်ရှိ တစ်ပိုင်းလျှပ်ကူးပစ္စည်း 95% ကျော်နှင့် ပေါင်းစပ်ပတ်လမ်းများ၏ 90% ကျော်ကို ဆီလီကွန် wafers များဖြင့် ပြုလုပ်ထားသည်။

မတူညီသော တစ်ခုတည်းသော ပုံဆောင်ခဲကြီးထွားမှုနည်းလမ်းများအရ၊ ဆီလီကွန်တစ်ခုတည်း ပုံဆောင်ခဲများကို Czochralski (CZ) နှင့် floating zone (FZ) ဟူ၍ နှစ်မျိုးခွဲခြားထားသည်။ ဆီလီကွန်ဝေဖာများကို အကြမ်းဖျင်းအားဖြင့် သုံးမျိုးခွဲခြားနိုင်သည်- polished wafers၊ epitaxial wafers နှင့် Silicon-On-insulator(SOI)။

ဆီလီကွန် ပွတ်တိုက် wafer ကို ရည်ညွှန်းသည်။ဆီလီကွန် waferမျက်နှာပြင်ကို polishing ဖြင့်ဖွဲ့စည်းထားသည်။ ၎င်းသည် 1 မီလီမီတာအောက် အထူရှိသော အဝိုင်း၊ ကြိတ်ခွဲခြင်း၊ ပွတ်တိုက်ခြင်း၊ သန့်ရှင်းရေး နှင့် အခြားပုံဆောင်ခဲတံတစ်ခု၏ အခြားလုပ်ငန်းစဉ်များဖြင့် ဆောင်ရွက်သော အဝိုင်းပြားဖြစ်သည်။ ၎င်းကို ပေါင်းစပ် circuit များနှင့် discrete devices များတွင် အဓိကအားဖြင့် အသုံးပြုကြပြီး ဆီမီးကွန်ဒတ်တာစက်မှုလုပ်ငန်းကွင်းဆက်တွင် အရေးကြီးသောရာထူးကို သိမ်းပိုက်ထားသည်။

ဖော့စဖရပ်စ်၊ ခနောက်စိမ်း၊ အာဆင်းနစ်စသည်ဖြင့် V အုပ်စုဒြပ်စင်များကို ဆီလီကွန်တစ်ခုတည်း ပုံဆောင်ခဲအဖြစ်သို့ ရောချသောအခါ၊ III အုပ်စုဝင် ဒြပ်စင်များဖြစ်သည့် ဘိုရွန်ကို ဆီလီကွန်ထဲသို့ ရောထည့်လိုက်သောအခါ၊ P-type လျှပ်ကူးပစ္စည်း ဖြစ်ပေါ်လာလိမ့်မည်။ silicon single crystals များ၏ ခံနိုင်ရည်အား doping ဒြပ်စင် ပမာဏ ဖြင့် ဆုံးဖြတ်သည် ။ တားမြစ်ဆေးပမာဏ များလေလေ၊ ခံနိုင်ရည်အား နည်းလေဖြစ်သည်။ ပေါ့ပေါ့ပါးပါး ရောထားသော ဆီလီကွန် ပွတ်တိုက် wafers များသည် ယေဘူယျအားဖြင့် 0.1W·cm ထက်ပိုသော ခံနိုင်ရည်ရှိသော ဆီလီကွန် ပွတ်ဆပ်ပြာမှုန့်များကို ရည်ညွှန်းပါသည်။ ပြင်းထန်စွာဆေးကြောထားသော ဆီလီကွန်ပွတ်တိုက် wafers များသည် ယေဘူယျအားဖြင့် 0.1W·cm ထက်နည်းသော ခံနိုင်ရည်ရှိသော ဆီလီကွန်ပွတ်ဝေဖာများကို ရည်ညွှန်းသည်၊ ၎င်းသည် ယေဘူယျအားဖြင့် epitaxial silicon wafers များအတွက် substrate material အဖြစ်အသုံးပြုကြပြီး semiconductor power devices များထုတ်လုပ်ရာတွင် တွင်ကျယ်စွာအသုံးပြုကြသည်။

ဆီလီကွန် ပေါ်လစီ wafer များ၎င်းသည် မျက်နှာပြင်ပေါ်တွင် သန့်ရှင်းသော ဧရိယာကို ဖန်တီးသည်။ဆီလီကွန် wafersannealing အပူကုသမှုပြီးနောက် silicon annealing wafers ဟုခေါ်ကြသည်။ အသုံးများသော အရာများ မှာ ဟိုက်ဒရိုဂျင် အနုစား wafer နှင့် အာဂွန် annealing wafer များ ဖြစ်သည်။ 300mm ဆီလီကွန် wafers နှင့် 200mm silicon wafers အချို့သည် ပိုမိုမြင့်မားသော လိုအပ်ချက်များဖြင့် double-sided polishing process ကိုအသုံးပြုရန်လိုအပ်ပါသည်။ ထို့ကြောင့်၊ silicon wafer ၏နောက်ကျောမှတဆင့် gettering centre ကိုမိတ်ဆက်ပေးသောပြင်ပ gettering နည်းပညာသည်အသုံးချရန်ခက်ခဲသည်။ အတွင်းပိုင်းရယူခြင်းစင်တာကိုဖွဲ့စည်းရန် annealing process ကိုအသုံးပြုသည့်အတွင်းပိုင်း gettering လုပ်ငန်းစဉ်သည် အရွယ်အစားကြီးမားသော ဆီလီကွန် wafers များအတွက် ပင်မရေစီးကြောင်းဖြစ်လာသည်။ ယေဘူယျ ပွတ်ထားသော wafers များနှင့် နှိုင်းယှဉ်ပါက၊ ပြုတ်ထားသော wafer များသည် စက်ပစ္စည်း၏ စွမ်းဆောင်ရည်ကို မြှင့်တင်နိုင်ပြီး အထွက်နှုန်းကို မြှင့်တင်ပေးကာ ဒစ်ဂျစ်တယ်နှင့် analog ပေါင်းစပ် circuit များနှင့် memory chips များ ထုတ်လုပ်ရာတွင် တွင်ကျယ်စွာ အသုံးပြုကြသည်။

တစ်ခုတည်းသောပုံဆောင်ခဲကြီးထွားမှုဇုန် အရည်ပျော်ခြင်း၏ အခြေခံနိယာမမှာ polycrystalline silicon rod နှင့် အောက်ရှိ တစ်ခုတည်းသော crystal များကြားတွင် အရည်ပျော်ဇုန်ကို ရပ်ဆိုင်းရန် အရည်ပျော်ခြင်း၏ မျက်နှာပြင်တင်းမာမှုကို အားကိုးပြီး သွန်းသောဇုန်အပေါ်သို့ ရွေ့လျားခြင်းဖြင့် ဆီလီကွန်တစ်ခုတည်းကို သန့်စင်ပြီး ကြီးထွားစေပါသည်။ ဇုံ အရည်ပျော်သော ဆီလီကွန် တစ်ခုတည်းသော ပုံဆောင်ခဲများသည် Crucibles များဖြင့် မညစ်ညမ်းဘဲ မြင့်မားသော သန့်စင်မှုရှိသည်။ ၎င်းတို့သည် 200Ω·cm ထက်မြင့်သော ခံနိုင်ရည်ရှိမှု နှင့် P-type silicon single crystals များ အပါအဝင် N-type silicon single crystals များ ထုတ်လုပ်ရန်အတွက် သင့်လျော်ပါသည်။ ဇုံအရည်ပျော်ခြင်းဆီလီကွန်တစ်ခုတည်းပုံဆောင်ခဲများကို ဗို့အားမြင့်နှင့် ပါဝါမြင့်ကိရိယာများထုတ်လုပ်ရာတွင် အဓိကအားဖြင့်အသုံးပြုကြသည်။

ဆီလီကွန် epitaxial waferအလွှာတစ်ခုပေါ်ရှိ အငွေ့အဆင့် epitaxial deposition ဖြင့် ဆီလီကွန်အလွှာတစ်ခု သို့မဟုတ် တစ်ခုထက်ပိုသော အလွှာများကို ရည်ညွှန်းပြီး ပေါင်းစပ် circuit များနှင့် discrete devices အမျိုးမျိုးကို ထုတ်လုပ်ရန် အဓိကအသုံးပြုသည်။

အဆင့်မြင့် CMOS ပေါင်းစည်းထားသော ဆားကစ်လုပ်ငန်းစဉ်များတွင်၊ ဂိတ်အောက်ဆိုဒ်အလွှာ၏ သမာဓိအားကောင်းလာစေရန်၊ ချန်နယ်အတွင်း ယိုစိမ့်မှုကို ပိုမိုကောင်းမွန်လာစေရန်နှင့် ပေါင်းစပ်ဆားကစ်များ၏ ယုံကြည်စိတ်ချရမှုကို မြှင့်တင်ရန်အတွက်၊ ဆီလီကွန် epitaxial wafers များကို မကြာခဏ အသုံးပြုလေ့ရှိသည်၊ ဆိုလိုသည်မှာ ဆီလီကွန်ပါးပါးဖလင်အလွှာတစ်ခုဖြစ်သည်။ မြင့်မားသော အောက်ဆီဂျင်ပါဝင်မှု ချို့ယွင်းချက်များနှင့် ယေဘူယျဆီလီကွန်ပွတ် wafers များ၏ မျက်နှာပြင်ရှိ ချို့ယွင်းချက်များစွာကို ရှောင်ရှားနိုင်သည့် ပေါ့ပေါ့ပါးပါး ရောထားသော ဆီလီကွန်ပွတ် wafer ပေါ်တွင် တစ်သားတည်းဖြစ်စေသော epitaxial ကို တစ်သားတည်းဖြစ်စေသည်။ ပါဝါပေါင်းစပ် circuit များနှင့် discrete စက်ပစ္စည်းများအတွက်အသုံးပြုသော ဆီလီကွန် epitaxial wafers များတွင်၊ မြင့်မားသောခံနိုင်ရည်ရှိသော epitaxial အလွှာသည် များသောအားဖြင့် epitaxial အလွှာကို ခံနိုင်ရည်နိမ့်သော ဆီလီကွန်အလွှာပေါ်တွင် ပေါက်ရောက်သည် (ပြင်းထန်စွာဆေးကြောထားသော ဆီလီကွန်ပွတ် wafer)။ စွမ်းအားမြင့် နှင့် ဗို့အားမြင့် အက်ပလီကေးရှင်းပတ်ဝန်းကျင်များတွင်၊ ဆီလီကွန်အလွှာ၏ ခံနိုင်ရည်နိမ့်မှုသည် on-resistance ကို လျှော့ချနိုင်ပြီး ခုခံမှုမြင့်မားသော epitaxial အလွှာသည် စက်၏ပြိုကွဲဗို့အားကို တိုးမြင့်စေနိုင်သည်။

SOI (ဆီလီကွန်-အင်စူလေတာ)စီလီကွန်သည် insulating layer တွင်ဖြစ်သည်။ ၎င်းသည် ထိပ်တန်းဆီလီကွန်အလွှာ (Top Silicon)၊ အလယ်ဆီလီကွန်ဒိုင်အောက်ဆိုဒ်မြှုပ်နှံထားသောအလွှာ (BOX) နှင့် အောက်ရှိ ဆီလီကွန်အလွှာပံ့ပိုးမှု (Handle) ပါရှိသော "sandwich" ဖွဲ့စည်းပုံဖြစ်သည်။ ပေါင်းစပ်ပတ်လမ်းထုတ်လုပ်ခြင်းအတွက် အလွှာအသစ်တစ်ခုအနေဖြင့်၊ SOI ၏အဓိကအားသာချက်မှာ အောက်ဆိုဒ်အလွှာမှတဆင့်လျှပ်စစ် insulation မြင့်မားစွာရရှိစေခြင်းဖြစ်ပြီး ၎င်းသည် parasitic capacitance နှင့် silicon wafers များ၏ယိုစိမ့်မှုကို ထိထိရောက်ရောက်လျှော့ချပေးမည့် မြင့်မားသောဆီလီကွန် wafers များထုတ်လုပ်မှုကို အထောက်အကူဖြစ်စေသည်။ အမြန်နှုန်း၊ ပါဝါနိမ့်၊ ပေါင်းစပ်မှုမြင့်မားပြီး ယုံကြည်စိတ်ချရမှု မြင့်မားသော အလွန်ကြီးမားသော ပေါင်းစပ်ဆားကစ်များဖြစ်ပြီး ဗို့အားမြင့်ပါဝါကိရိယာများ၊ optical passive ကိရိယာများ၊ MEMS နှင့် အခြားနယ်ပယ်များတွင် တွင်ကျယ်စွာ အသုံးပြုပါသည်။ လက်ရှိတွင် SOI ပစ္စည်းများ၏ ပြင်ဆင်မှုနည်းပညာတွင် အဓိကအားဖြင့် bonding technology (BESOI)၊ smart stripping technology (Smart-Cut)၊ oxygen ion implantation technology (SIMOX)၊ oxygen injection bonding technology (Simbond) စသည်တို့ ပါဝင်သည်။ ထုတ်ယူနည်းပညာ။

SOI ဆီလီကွန် ဝေဖာများပါးလွှာသောဖလင် SOI ဆီလီကွန်ဝေဖာများနှင့် အထူ-ဖလင် SOI ဆီလီကွန်ဝေဖာများ ဟူ၍ ထပ်မံခွဲခြားနိုင်သည်။ ထိပ်ဆီလီကွန်အထူ - ပါးလွှာသောဖလင်SOI ဆီလီကွန် ဝေဖာများ1um ထက်နည်းသည်။ လက်ရှိတွင်၊ ပါးလွှာသောဖလင် SOI ဆီလီကွန် wafer စျေးကွက်၏ 95% ကို 200mm နှင့် 300mm အရွယ်အစားများတွင် စုစည်းထားပြီး ၎င်း၏စျေးကွက်မောင်းနှင်အားသည် အဓိကအားဖြင့် မြန်နှုန်းမြင့်၊ ပါဝါနိမ့်ထုတ်ကုန်များ၊ အထူးသဖြင့် မိုက်ခရိုပရိုဆက်ဆာအပလီကေးရှင်းများမှဖြစ်သည်။ ဥပမာအားဖြင့်၊ 28nm အောက်အဆင့်မြင့်လုပ်ငန်းစဉ်များတွင်၊ insulator (FD-SOI) တွင် အပြည့်အ၀ ကုန်ဆုံးသွားသော ဆီလီကွန်များသည် ပါဝါသုံးစွဲမှုနည်းခြင်း၊ ဓာတ်ရောင်ခြည်ကာကွယ်ခြင်းနှင့် အပူချိန်မြင့်မားခြင်း၏ ထင်ရှားသောစွမ်းဆောင်ရည်အားသာချက်များရှိသည်။ တစ်ချိန်တည်းမှာပင်၊ SOI ဖြေရှင်းချက်များကိုအသုံးပြုခြင်းသည် ကုန်ထုတ်လုပ်မှုလုပ်ငန်းစဉ်ကို များစွာလျှော့ချနိုင်သည်။ အထူ-ဖလင် SOI ဆီလီကွန်ဝေဖာများ၏ ထိပ်တန်းဆီလီကွန်အထူသည် 1um ထက်ကြီးပြီး မြှုပ်ထားသောအလွှာ၏အထူမှာ 0.5-4um ဖြစ်သည်။ အထူးသဖြင့် စက်မှုထိန်းချုပ်မှု၊ မော်တော်ယာဥ်အီလက်ထရွန်းနစ်၊ ကြိုးမဲ့ဆက်သွယ်ရေးစသည်ဖြင့် ပါဝါစက်ပစ္စည်းများနှင့် MEMS နယ်ပယ်များတွင် အဓိကအားဖြင့် အသုံးပြုကြပြီး များသောအားဖြင့် 150mm နှင့် 200mm အချင်းထုတ်ကုန်များကို အသုံးပြုကြသည်။